Wyzwanie

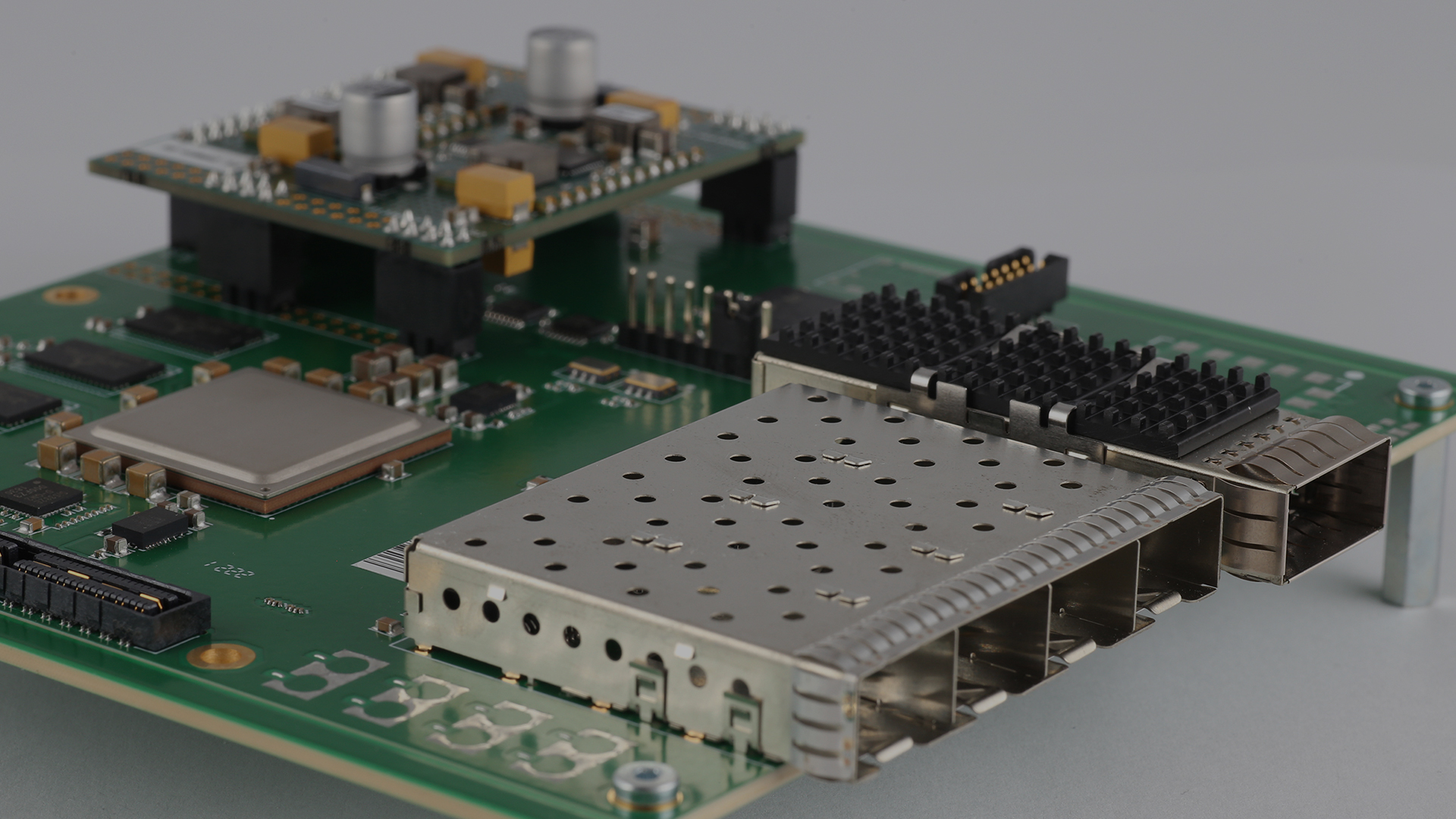

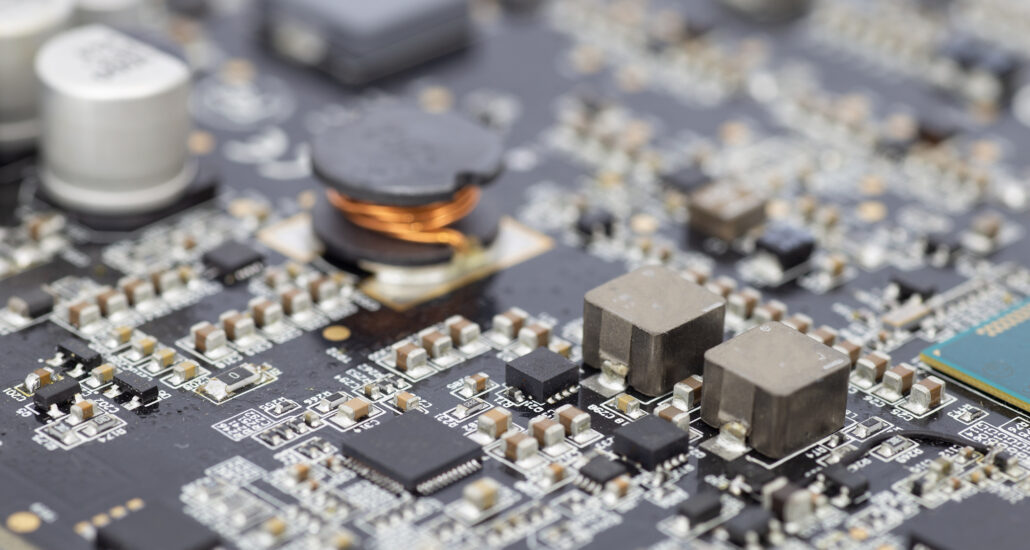

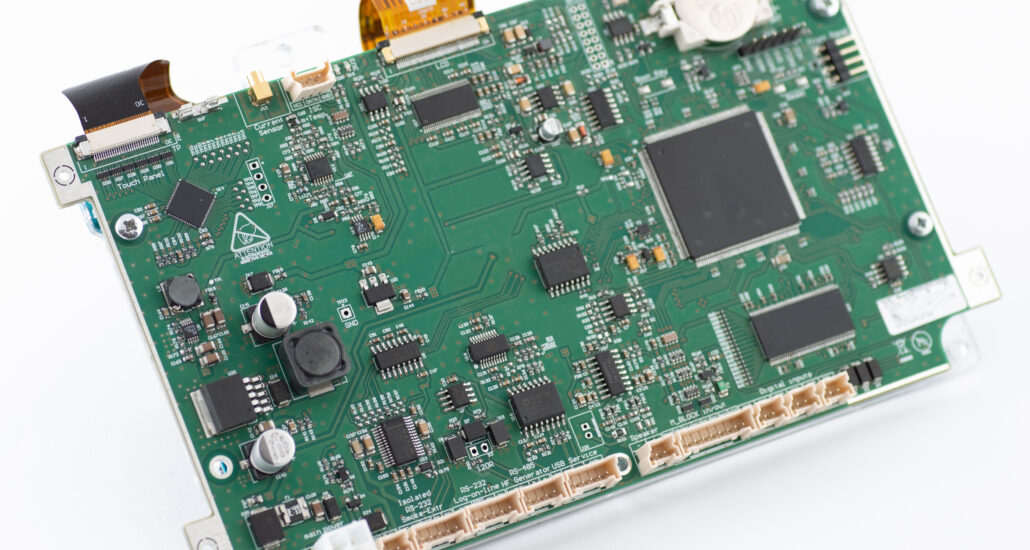

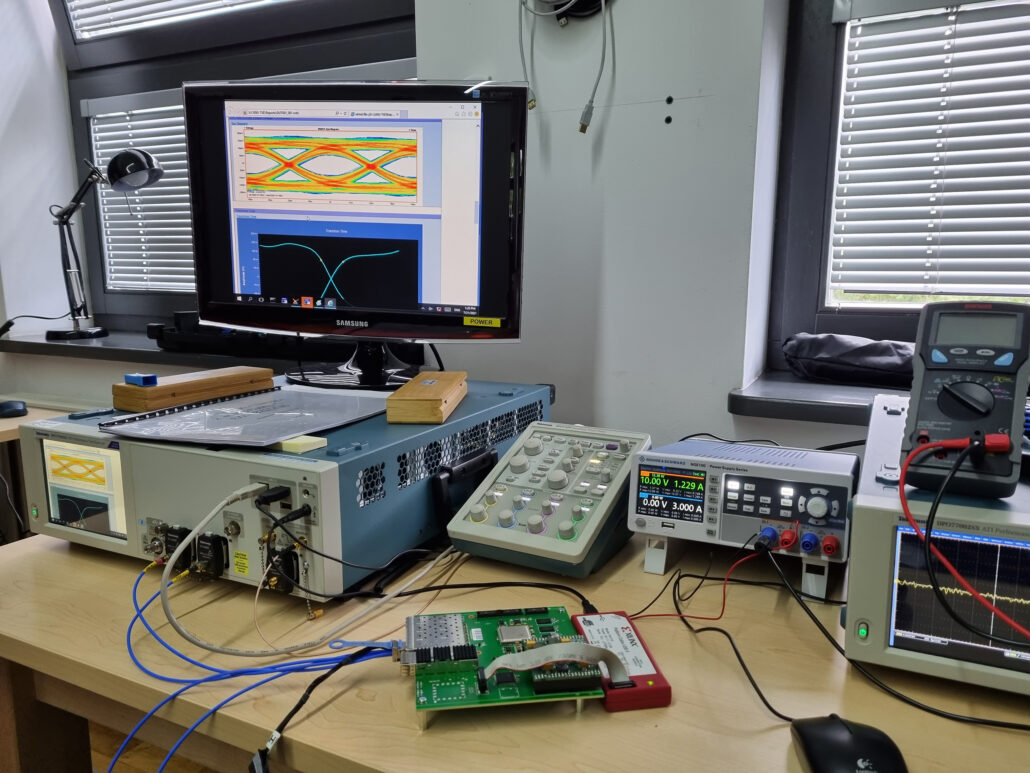

Niniejszy projekt dotyczył weryfikacji procesu projektowego urządzeń elektronicznych zawierających ultra-szybkie interfejsy cyfrowe. Nadrzędnym wymaganiem było rozszerzenie procesu projektowego o szerokopasmowe symulacje zjawisk integralności sygnałowej i mocy (SI/PI), a także dobór i weryfikacja instrumentarium w celu późniejszej weryfikacji pomiarowej. Kluczowymi elementami projektu były: projekt kuponu impedancyjnego (IC) zawierającego wybrane elementy routingu wysokiej gęstości tzw. HDI (High Density Interconnect), projekt Układu Testowego – eksperymentalnego urządzenia elektronicznego – do weryfikacji funkcjonalnej interfejsów SFP+, QSFP28 oraz DDR4. W ramach projektu wykonano symulacje i pomiary kuponu oraz połączeń szybkich Układu Testowego, tj. transceiverów 25Gbps (NRZ) wykorzystując zintegrowany układ FPGA Xilinx Kintex Ultrascale+. Projekt powstawał na zlecenie jednego z polskich operatorów telekomunikacyjnych i był fazą rozpoznania technologicznego dla szczególnie zaawansowanych projektów elektronicznych.

„Największym wyzwaniem projektu były multi-gigabitowe szybkości interfejsów i związane z nimi bardzo szerokie pasmo symulacji i pomiarów sięgające 40GHz. Należało odpowiednio przeprowadzić dobór Instrumentarium uwzględniając nie tylko same urządzenia pomiarowe, ale także niezbędne akcesoria i metodyki pomiarowe. Całość miała prowadzić do weryfikacji zbieżności wyników symulatora z rzeczywistością i potwierdzenia prawidłowości procesu projektowego – co ostatecznie zakończyło się sukcesem.”

Kamil Grabowski, CEO

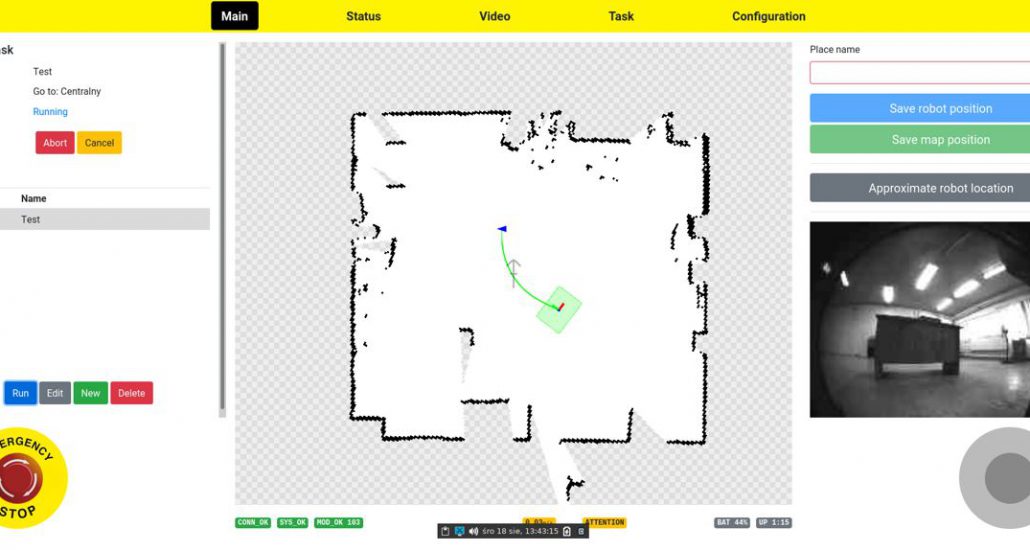

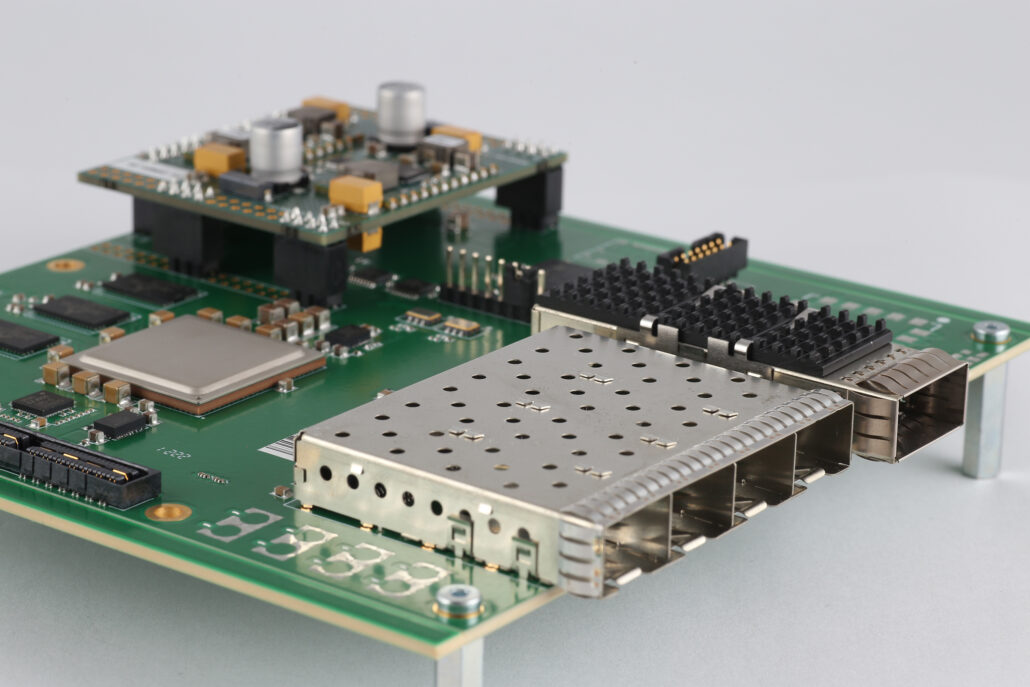

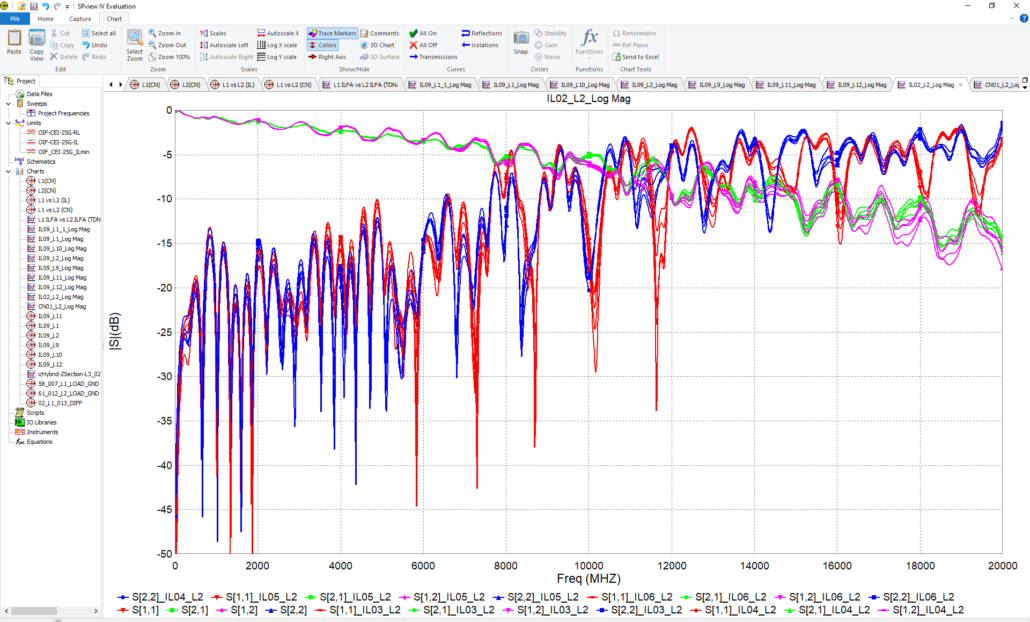

Projekt wymagał wykonania ogromnej pracy związanej z pozyskaniem zasadniczo nowej i zaawansowanej wiedzy w dość krótkim czasie. Dokonano rozpoznania narzędzi symulacyjnych SI/PI i przeprowadzono symulacje funkcjonalne i ekstrakcje modeli czwórnikowych wybranych połączeń UT i linii testowych IC (głównie w Cadence Sigrity 2019). Aby móc potwierdzić fizykalność realizacji interfejsów wykonano w pełni funkcjonalny obwód elektroniczny zawierający układ FPGA Xilinx Kintex US+ umożliwiający komunikację transceiverami z szybkością 25Gbps. Wykorzystano zaawansowane materiały ISOLA do projektu stosu i wykonania PCB. W następnych krokach z sukcesem uruchomiono UT, przeprowadzono i potwierdzono zgodność ze standardami IEEE802.3 CAUI4 i JEDEC-DDR4 interfejsów wkładek optycznych SFP+ i QSFP, wykorzystując dedykowane fikstury pomiarowe, szerokopasmowe sondy i specjalizowane oprogramowanie do testów zgodności (compliance). Kupon impedancyjny poddano pomiarom TDR w celu uzyskania parametrów czwórnikowych (Time Domain Network Analysis) do walidacji jakości wykonania linii mikropaskowych. Wprowadzono własną metodykę oceny jakości laminatów pod kątem szybkich interfejsów cyfrowych aby ostatecznie zestawić wyniki pomiarów z symulacjami.

Wyniki i Korzyści

W ramach projektu potwierdzono fizykalność wykonania szybkich interfejsów cyfrowych w zaproponowanym procesie wytwórczym, wzbogaconym o etapy zaawansowanych symulacji SI/PI i pomiarów:

- Potwierdzono proces wytwórczy dla zaawansowanych obwodów elektronicznych oraz synergię kilku narzędzi CAD/EDA.

- Wykonano symulacje zjawisk SI/PI, rozpoznano problemy i ograniczenia

- Rozpoznano i zweryfikowano instrumentarium niezbędne do pomiarów szerokopasmowych (właściwych dla multi-gigabitowych linków cyfrowych)

- Opracowano metodykę porównania jakości laminatów dla połączeń multi-gigabitowych, wyłoniono podwykonawców do produkcji laminatów PCB.

- Dokonano rozeznania technologicznego, zbudowano unikalne kompetencje i potwierdzono możliwość realizacji projektów zwierających interfejsy o szybkościach sięgających setek gigabitów na sekundę.

Kluczowe Rozwiązania

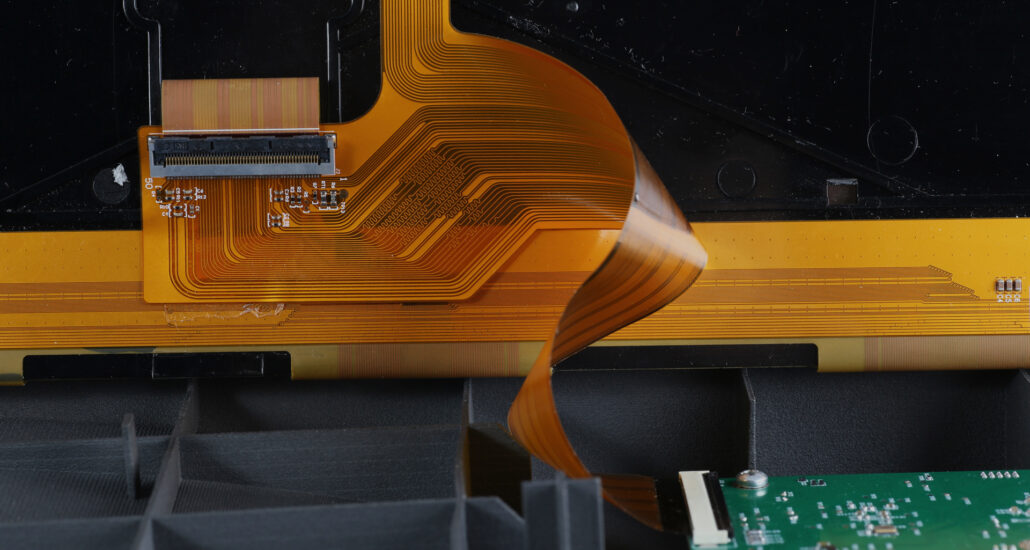

- Zaprojektowano i z sukcesem wykonano stos 14 warstwowy na specjalistycznym materiale ISOLA dedykowanym do interfejsów o wysokiej przepływności, a także wykorzystano elementy HDI;

- Wykonano i z sukcesem uruchomiono układ testowy zawierający układ Kintex US+

- Osiągnięto przepływności interfejsu na poziomie 100Gbps (CAUI4, QSFP)

- Przeprowadzono symulacje zjawisk SI/PI w paśmie do 25GHz

- Wykonano pomiary szerokopasmowe w dziedzinie czasu interfejsów GTY dla 25Gbps (wykresy oka, dekompozycja jittera, szumy, przesłuchy, etc.), dokonano symulacyjnej i pomiarowej ekstrakcji macierzy rozproszenia linii mikropaskowych w paśmie do 40GHz (TDNA)

- Pozyskano część wymaganego instrumentarium na potrzeby dalszych prac.

Wolumen i zasięg

Projekt badawczo-rozwojowy.